用于PCB质量验证的时域串扰测量法

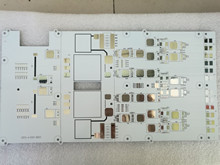

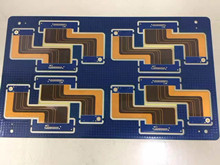

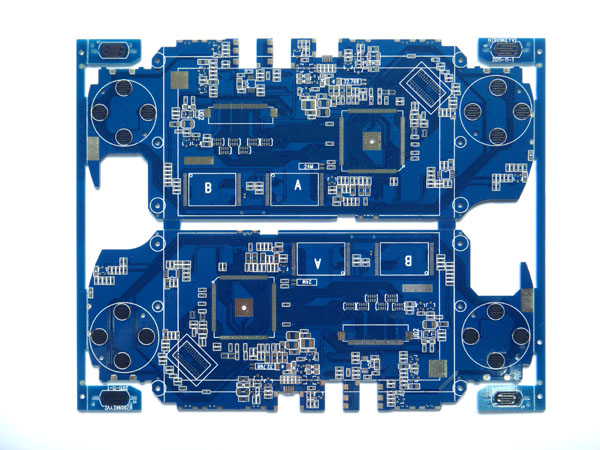

随着通讯、视讯、网络和计算机技术领域中数字系统的执行速度日益加速,对此类系统中的印刷电路板(PCB)的质量要求也越来越高。早期的PCB设计在面临讯号频率日益增高和脉冲上升时间日益缩短的情况下,已无法保证系统性能和工作要求。在目前的PCB设计中,我们必须利用传输线理论对PCB及其组件(边缘连接器、微带线和零组件插座)进行建模。只有充分了解PCB上串扰产生的形式、机制和后果,并采用相应技术最大程度地加以抑制,才能帮助我们提高包含PCB在内的系统的可靠性。本文主要围绕PCB设计展开,但相信文中所讨论的内容也有助于电缆和连接器的表征等其它应用场合使用。

PCB设计师之所以关心串扰这一现象,是因为串扰可能造成以下性能方面的问题:噪音电平升高;有害尖峰突波;数据边沿抖动;意外的讯号反射。

这几个问题中哪些会对PCB设计有所影响取决于多方面因素,如板上所用逻辑电路的特性、电路板的设计、串扰的模式(反向或前向)以及干扰线和被干扰线两边的端接情况。本文提供的信息可协助读者加深对串扰的认识和研究,减少串扰对设计影响。

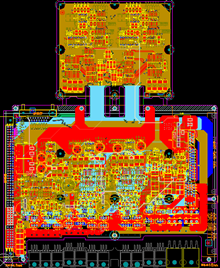

为了尽可能减少PCB设计中的串扰,我们必须在容抗和感抗之间寻找平衡点,力求达到额定阻抗值,因为PCB的可制造性要求传输线阻抗得到良好控制。在电路板设计完成之后,板上的组件、连接器和端接方式决定了哪种类型的串扰会对电路性能产生多大的影响。利用时域测量方法,透过计算拐点频率和理解PCB串扰(Crosstalk-on-PCB)模型,可以帮助设计人员设置串扰分析的边界范围。

关注[恒成和线路板]微信公众平台,了解更多行业资讯和最新动态!(微信号:PCBHCH)

同类文章排行

- 车用PCB行业是一个拥有巨大发展潜力的板块

- 中国PCB行业增速高于全球平均水平

- 芯片如何焊接在电路板上?

- FPC柔性线路板在可穿戴设备中的应用优势分析

- 如何清洁电路板?

- 关于多层PCB线路板的诞生

- 如何避免FPC连接器断裂?

- FPC制程中常见缺陷和解决方案

- PCB过孔为什么不能打在焊盘上?

- 柔性线路板三种主要功能叙述

最新资讯文章

- 车用PCB行业是一个拥有巨大发展潜力的板块

- 中国PCB行业增速高于全球平均水平

- 芯片如何焊接在电路板上?

- FPC柔性线路板在可穿戴设备中的应用优势分析

- 如何清洁电路板?

- 关于多层PCB线路板的诞生

- 如何避免FPC连接器断裂?

- FPC制程中常见缺陷和解决方案

- PCB过孔为什么不能打在焊盘上?

- 柔性线路板三种主要功能叙述

您的浏览历史

阿里巴巴

阿里巴巴

新浪微博

新浪微博 腾讯微博

腾讯微博